# El circuito electrónico

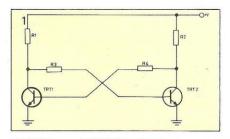

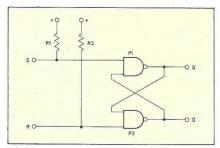

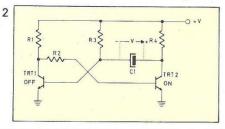

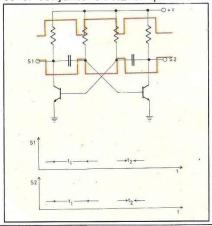

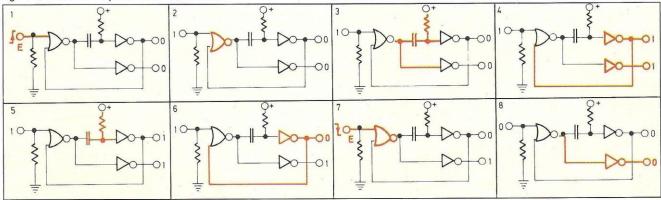

Si dos transistores funcionando en configuración de emisor común se montan acoplados entre sí de forma que la salida de uno esté conectada a la entrada del otro, y viceversa, se puede lograr un circuito con características muy peculiares (figura 1).

Cuando el circuito mencionado se pone bajo tensión, si ambos transistores son iguales se polarizarán de tal forma que funcionen como amplificadores.

Supongamos que en un momento determinado se produce un ligero aumento de tensión en la base de TRT1 (debido, por ejemplo, al ruido generado por los propios componentes). Tal aumento será amplificado por el transistor, apareciendo una disminución de tensión en su colector (inversión

de fase entrada-salida) de mayor amplitud que el cambio en la base (ganancia).

Como el colector de TRT1 está unido a la base de TRT2 (a través de una resistencia de polarización), en esta base aparecerá una disminución de tensión, disminución que será amplificada, y la encontraremos en su colector con mayor amplitud y en forma de aumento de tensión (ganancia e inversión de fase).

Este aumento aparecerá de nuevo en la base de TRT1 (origen de la variación), pero con mucha mayor amplitud que el primero que se produjo (ganancia de dos etapas), con lo que el proceso explicado volverá a repetirse sucesivas veces. Observemos que tal proceso tiende a aumentar la tensión del colector TRT2 y a disminuir la del colector de TRT1 indefinidamente.

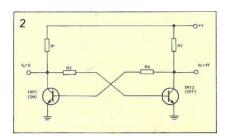

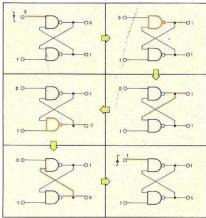

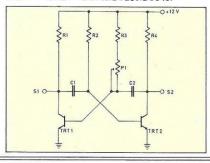

¿Cuándo cesa este fenómeno? Pues parece claro que cuando la tensión del colector de TRT2 no pueda subir más, ni cuando a la del colector de TRT1 le sea posible bajar más. Esto es lo mismo que decir que el transistor TRT1 irá a saturación y el TRT2 a corte (figura 2).

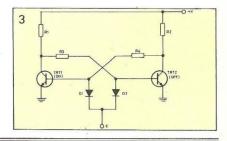

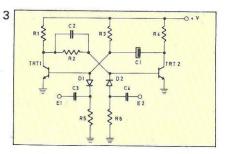

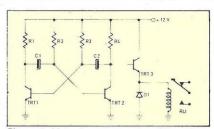

¿ Puede sacarse al circuito de esta situación estable? Sí se puede, y vamos a ver cómo. Modifiquemos el circuito anterior añadiendo un par de diodos conectados como indica la figura 3, y veamos qué ocurre cuando sobre la entrada E se aplica un *impul*so negativo.

Sobre el transistor TRT2, tal impulso no tendrá efecto alguno, puesto que se encuentra cortado, y el impulso no puede llevarlo más allá del corte. Sin embargo, como TRT1 está en conducción (saturado), un impulso negativo en su base tenderá a ser amplifi-

cado por él, apareciendo en su colector un impulso positivo (debido a la inversión de fase) o, lo que es igual, una tendencia a aumentar la tensión del colector de TRT1.

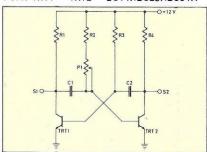

Como puede verse, se inicia un proceso inverso al que se describió anteriormente, y cuyo final previsible y lógico acabará con la saturación de TRT2 y el corte de TRT1, es decir, la situación exactamente opuesta a la anterior (figura 4). Puesto que el círculo es totalmente simétrico, esta nueva situación o estado del mismo será igual de estable que el anterior. Así, el circuito descrito tiene dos, y sólo dos, estados posibles (TRT1 = ON y TRT2 = OFF; TRT1 = OFF y TRT2 = ON). Además, ambos son estables y en cualquiera de ellos el circuito puede permanecer indefinidamente. Es por esta razón que tal circuito se denomina biestable.

Este circuito se utiliza muchas veces como divisor de frecuencia.

Tomemos como salida uno de los colectores, por ejemplo, el de TRT2 y supongamos que el circuito está en el estado que presenta la figura 4. El primer impulso negativo irá a TRT2, haciendo que su colector adquiera una tensión positiva. El segundo impulso negativo aplicado a E irá ahora para TRT1, provocando su corte, y,

consecuentemente, la saturación de TRT2. Esto significa que la tensión de su colector (que hemos tomado como salida) irá hacia cero de nuevo, o sea, aparecerá un impulso negativo en la salida.

Los nuevos impulsos sobre E repetirán el proceso explicado en el párrafo anterior. Pero observemos una cosa: en la salida sólo aparecerá un impulso negativo (paso de + V a O) en los instantes correspondientes a los impulsos que hagan lugar par en la entrada (esto es, el segundo, cuarto, sexto, etc.). Esto es lo mismo que decir que la señal de salida tiene una frecuencia mitad que la de la entrada. Es decir, un biestable se comporta como un divisor de frecuencia.

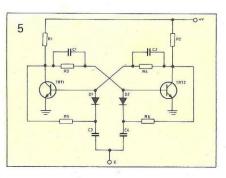

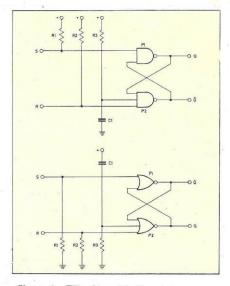

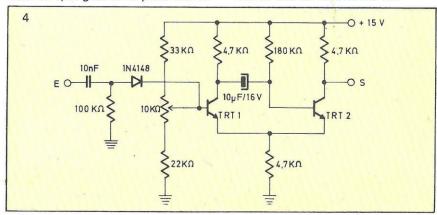

El circuito biestable mostrado es el más sencillo que puede utilizarse. Pueden introducirse mejoras que aseguren la estabilidad de los estados y/o la rapidez y seguridad del cambio de uno a otro. Algunas de tales mejoras se muestran en la figura 5).

Los condensadores C1 y C2 ayudan a que el cambio de estado se realice con mucha mayor rapidez y seguridad. Los marcados como C3 y C4 hacen que a las bases de los transistores lleguen sólo *impulsos* y no *niveles* de tensión, con lo que se hace más seguro el disparo.

Por su parte, las resistencias R5 y R6 polarizan a los diodos D1 y D2 de tal forma que sólo entre en conducción aquél de los dos unido a la base del transistor que deba recibir el impulso negativo, con lo que el cambio de estado, o disparo, se hace con plena sequridad.

Ya se ha dicho en otro lugar que un biestable es un circuito eléctrico o electrónico que posee dos estados diferenciados y perfectamente estables (pueden permanecer en cada uno de ellos durante un tiempo indefinido). Existen muchas formas de materializar esta idea: un relé tiene dos posiciones estables; un conmutador también tiene dos (o más) posiciones estables; un circuito con dos transistores en cascada también puede formar un biestable.

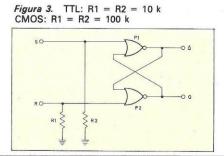

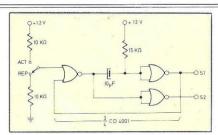

Dada la tendencia a la integración de circuitos que existe hoy día, y el bajo precio que tienen los componentes que los incorporan, resulta muy útil poder disponer de un biestable con puertas lógicas. El circuito más sencillo que puede construirse se muestra en la figura 1, y consta de tan

sólo dos puertas NAND.

El funcionamiento es muy senci-Ilo. Cuando sobre las entradas S y R no se aplica señal alguna, las resistencias R1 y R2 hacen positivas las respectivas entradas de las puertas P1 y P2. Si se supone, por ejemplo, que la salida de P1 (señal Q) es «1», sobre las entradas de la puerta P2 hay aplicados niveles «1», por lo que su salida (Q) será «0». Como tal sa-

Figura 1. TTL: R1 = R2 = 10 k; CMOS: R1 = R2 = 100 k

lida se conecta a una de las entradas de la otra puerta, obliga a que la salida de dicha puerta se mantenga en

Figura 2.

«1». Obsérvese que esta situación (Q = 1; Q = 0) es estable indefini-

Si en lugar de ser Q = 1, como se ha supuesto, hubiera sido Q = 0, este nivel lógico se aplicaría a una de las entradas de P2, obligando a su salida a adoptar el nivel «1» (Q = 1). A su vez, el nivel de esta salida, junto con el proporcionado por R1, hacen que la salida de P1 permanezca en «0» (Q = 0). Tal situación (opuesta a la anterior) es igualmente estable. Por tanto, el circuito puede calificarse como biestable.

## Modificación del estado

¿Puede llevarse el biestable descrito de un estado a otro de los estables? Sí, y para ello se incluyen las entradas R y S. Supongamos que la salida de P1 es «0» (Q = 0;  $\overline{Q}$  = 1) y que se aplica un impulso negativo o un nivel «0» sobre la entrada S (se hace S = 0). A las entradas de la puerta P1 habrá aplicados un «0» (S) y un «1» (Q), por lo que su salida se verá forzada a adoptar el nivel «1» (Q = 1).

En las entradas de P2 aparecerán ahora dos niveles «1» (el creado en Q, y el provocado por R2), con lo que su salida irá a nivel lógico «0»

(Q = 0). Este nivel se aplicará a la puerta P1, lo que «bloqueará» su salida en el valor «1» (Q = 1), aunque sobre la entrada S deje de aplicarse el nivel «0» o desaparezca el impulso negativo que provocó el cambio de estado del biestable (figura 2).

Este nuevo estado adquirido no se modifica, aunque vuelvan a aplicarse a la entrada S nuevos impulsos negativos. Sin embargo, cambiará de estado cuando tal impulso se aplique a la entrada R, provocando que el biestable «bascule» hacia el estado opuesto (Q = 0; $\overline{Q} = 1$ ). Obsérvese que siempre que se aplique un impulso negativo (o nivel lógico «0») a la entrada S, la salida Q adoptará el nivel «1», y siempre que tal impulso se aplique a R, la salida Q adoptará el nivel «0» (la salida Q siempre tiene el nivel lógico opuesto al de Q).

Es por esta característica que este tipo de biestable se denomina R-S, proviniendo tal nomenclatura de las iniciales de los términos «reset» y «set» que podrían traducirse (muy libremente) como puesta a cero y posicionado, dado que el estado que adopta la salida Q (que puede considerarse como salida principal del biestable) se corresponde con el nivel presente en tales entradas (R = 0 hace Q = 0; S = 0 hace Q = 1).

# Empleo de puertas NOR

Si en lugar de emplear puertas NAND se emplean puertas NOR, el circuito básico a montar es el mostrado en la figura 3, en el que existen algunas diferencias con el anterior. La más evidente es la conexión de las resistencias R1 y R2 a masa, en lugar de al positivo de alimentación. Por otro lado, las salidas Q y Q ocupan lugares opuestos a los de antes; y, por fin, para cambiar el biestable de estado es necesario aplicar a la entrada R o S (la que corresponda) un impulso positivo o nivel lógico «1» (al contrario que antes). Por lo demás, el funcionamiento es idén-

Figura 4. TTL: C1 = 10 nF, R1 = R2 = R3 = 10 kCMOS: C1 = 10 nF, R1 = R2 = R3 = 100 k

tico, teniendo en cuenta que las puertas son de tipo NOR. La entrada R sirve para hacer Q = 0, mientras que la S hace Q = 1.

Finalmente, en la figura 4 se muestran dos circuitos que adoptan el estado «reset» (Q = 0;  $\overline{Q} = 1$ ) cuando se conecta la tensión de alimentación.

El circuito más elemental de un monoestable se da en la figura 1. Supongamos que TRT1 está saturado. Su tensión de colector será prácticamente igual que la del emisor (unido a masa), por lo que mantendrá a TRT2 cortado. El condensador C1 se encontrará cargado con una tensión aproximadamente igual a la de alimentación. En esta situación, el circuito puede permanecer por un tiempo indefinido; es, por tanto, un estado estable.

Cuando se aplica un impulso negativo a la entrada E, el transistor TRT1 tenderá a amplificarlo, por lo que aparecerá en su colector invertido de signo (impulso positivo). Tal impulso es llevado gracias a R2, a la base de TRT2, quien lo amplificará e invertirá de nuevo, apareciendo en su colector como impulso negativo.

Como puede verse, el funcionamiento es totalmente similar al de un biestable, por lo que la condición a que tenderá el circuito es a que TR1 vaya al corte, y TRT2 se sature (figura 2). Pero existe una diferencia básica, y es que en un monoestable está C1 en el circuito, que no ha podido descargarse durante el proceso explicado, dada la rapidez con que se produce.

## El estado semiestable

Obsérvese que al estar TRT2 saturado, el terminal positivo de C1 está virtualmente conectado a masa (VcE= 0), por lo que tenderá a cargarse a través de R3 hasta una tensión igual a la de alimentación (con la polaridad cambiada sobre sus terminales). Tal proceso supone que, primero, se descargue hasta que la tensión en sus bornes sea nula, para, posteriormente, comenzar a cargarse en sentido opuesto. Pero como el terminal negativo de C1 está conectado a la base de TRT1, cuando la tensión sobre el condensador pase por cero y comience a hacerse de signo opuesto, el transistor TRT1 comenzará a conducir (por adquirir su base un

potencial positivo respecto de su emisor, que está a masa). Esto hará que sobre su colector aparezca una disminución de tensión (amplificación e inversión), que será llevada a TRT2, iniciándose un nuevo proceso de basculamiento en sentido opuesto al de antes, que acabará con TRT1 saturado y TRT2 en corte. Como puede verse, el segundo estado del circuito presentado (TRT1= OFF; TR2= ON) no es estable indefinidamente, sino tan sólo durante un cierto tiempo, que puede calcularse, aproximadamente, con ayuda de la fórmula:

T= 0,7·C1·R3 de forma que T viene dado en milisegundos (ms), cuando C1 se pone en microfarradios (μF) y R3 en Kilohmios (kΩ). Así, por ejemplo, para C1= 10 μF y R3= 150 kΩ, T vale: T= 0,7·10·150=150 ms ≈ 1 segundo Por tanto, el circuito de la figura 1

tiene un solo estado estable; de ahí 3 su nombre: monoestable. Y una propiedad interesante; el tiempo que está en su estado temporalmente estable sólo depende de los valores dados a los componentes del circuito.

### Mejoras en el circuito

Pueden añadirse algunos elementos que mejoren algunos aspectos del funcionamiento del circuito básico. En la figura 3 se muestran algunos de ellos. El condensador C2 sirve para acelerar la transición del estado estable al semiestable. El monoestable puede dispararse con impulsos o tensiones *negativas* aplicadas a la entrada E1, o bien con impulsos o tensiones *positivas* aplicadas a E2. A ello colaboran las redes C3-R5-D1 y C4-R6-D2, respectivamente.

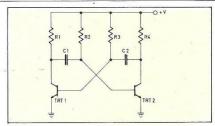

Otra mejora que puede hacerse es con el circuito mostrado en la figura 4, en el que el acoplo entre los transistores es a través de los respectivos emisores. En el estado estable, TRT1 está cortado y TRT2 en saturación. Aplicando un impulso positivo a la entrada E, el monoestable entra en su estado semiestable, con TRT1 conduciendo (no en saturación) y TRT2 cortado. El condensa-

dor C1 actúa de forma similar a la de antes, haciendo bascular al circuito a su estado anterior.

La novedad de este circuito, aparte de su configuración distinta, consiste en que gracias al potenciómetro R1 puede variarse la duración del estado semiestable, entre 200 milisegundos y 1 segundo, según que el cursor esté en su parte inferior o en la superior, respectivamente, y con los valores de los componentes mostrados en el esquema. Como transistores puede emplearse cualquier modelo de silicio de alta ganancia (BC147/ BC237 /BC557), obteniéndose en la salida S un impulso positivo de unos 7 V de amplitud (nivel superior del impulso en 15 V). La variación en la duración del estado semiestable es lineal aproximadamente con la resistencia R1.

## **Fundamento**

Los circuitos básicos correspondientes a un monoestable y a un biestable son muy similares, hasta el punto de que aquél puede obtenerse de éste cambiando tan sólo una resistencia por un condensador. Este último componente añade un cierto grado de inestabilidad al conjunto, debido al tiempo que emplea en su carga/descarga.

Si se añade un segundo condensador a un monoestable, tal como se muestra en la figura, 1, se conseguirá que el circuito tenga dos estados semiestables (igual que el monoestable tiene uno); esto equivale a decir que ninguno de los dos estados posibles del circuito es estable indefinidamente, sino que tan sólo lo es temporalmente. De aquí que tal circuito reciba la denominación de astable (de a-, que indica negación, y -estable).

El funcionamiento del circuito es muy similar al ya descrito para el monoestable, y consiste básicamente en que el transistor TRT1 se mantiene en corte, mientras que C2 se descarga a través de R3, estando TRT2 saturado. El circuito permanece en tal estado durante un

tiempo que viene dado, aproximadamente, por la expresión:

$$t_1 = 0.7 \cdot C2 \cdot R3$$

Pasado este tiempo, el circuito bascula, de forma que TRT1 entra en saturación y TRT2 en corte. Ahora es el conjunto C1-R2 el que inter-

viene en la duración del nuevo estado, viniendo dado el tiempo en que permanece en el mismo por:

$$t_2 = 0.7 \cdot C1 \cdot R2$$

de forma que, de nuevo, el circuito cambiará al estado anterior. El proceso se repetirá indefinidamente, pudiéndose obtener de los colectores de ambos transistores las formas de onda mostradas en la figura 2. Obsérvese que los dos tiempos que intervienen en el proceso no tienen por qué ser iguales.

Si se hace que los valores de C1 y C2 sean iguales, y lo mismo ocurre con R2 y R3, entonces sí que t<sub>1</sub> y t<sub>2</sub> serán iguales y las ondas obtenidas de los colectores serán *cuadradas* (igual duración del estado alto y el bajo), pudiéndose calcular la *frecuencia* de tales ondas (son iguales, aunque complementarias) de la expresión:

$$f = \frac{0.7}{R \cdot C}$$

siendo R el valor ohmico de R2 o R3, y C la capacidad de C1 o C2.

## Modificaciones

El circuito básico arriba presentado es muy seguro y regular en su fun-

cionamiento, a pesar de su extrema sencillez. Por lo general, cuando se necesita un multivibrador es para utilizar sus formas de onda para alguna aplicación práctica (por ejemplo, encender y apagar luces, actuar de mando para algún otro circuito, etc.). Aunque en muchos casos la tensión de gobierno para tales aplicaciones puede tomarse directamente de los colectores (puntos S1 y S2 de la figura 2), en otras ocasiones no es factible hacerlo.

En la figura 3 se muestra un circuito que gobierna un relé, los contactos del cual pueden a su vez servir para mandar cualquier señal. Con los valores mostrados, los contactos permanecerán cerrados medio se-

Figura 4. Lista de componentes: R1 = R4 =  $1 \text{ k}\Omega$ . R2 = R3 =  $18 \text{ k}\Omega$ . R5 =  $10 \text{ k}\Omega$ . C1 = C2 = 39 nF, disco. TRT1 a TRT3 = BC147/BC237-BC547.

gundo, y abiertos otro medio segundo en ciclos repetitivos.

Con el circuito de la figura 4 puede gobernarse la oscilación del multivibrador, por medio de una señal digital aplicada sobre la entrada E. Cuando tal señal es (0), el circuito no oscila, mientras que cuando se aplica un «1» el multivibrador entrega en la salida S una señal cuadrada de 1 kHz.

El circuito de la figura 5 entrega en la salida S2 impulsos positivos (negativos en S1) de 10 µseg de duración, con una frecuencia que puede variarse entre 200 Hz y 20 kHz, con ayuda del potenciómetro P1. En cambio, con el circuito de la figura 6 se obtiene una serie de impulsos

Figura 5. Lista de componentes: R1 = R3 = R4 = 10 k $\Omega$ . R2 = 56 k $\Omega$ . P1 = 1 M $\Omega$ , lineal s/int. C1 = 270 pF, cerámico. C2 = 5,6 nF, cerámico. TRT1 = TRT2 = BC149/BC239/BC549.

Figura 3. Lista de componentes: R1 = R4 = 3,3 kΩ. R2 = R3 = 68 kΩ. C1 = C2 = 10 μF − 16 V, electrolíticos. TRT1 a TRT3 = BC147-BC237/BC547. D1 = 1N4148/1N4001. RL1 = Relé 12V − 160 Ω.

negativos de S1 (positivos de S2), cuya duración puede variarse entre 10 y 100 µseg con ayuda del potenciómetro P1. La frecuencia de repetición de los mismos es de 1 kHz, aproximadamente.

Figura 6. Lista de componentes: R1 = R4 = 3,3 kΩ. R2 = 5,6 kΩ. R3 = 33 kΩ. P1 = 50 kΩ, lineal s/int. C1 = 2,7 nF, cerámico. C2 = 39 nF, disco. TRT1 = TRT2 = BC147/BC237/BC547.

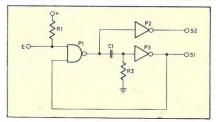

El circuito es el mostrado en la figura 1. En reposo, las dos salidas S1 y S2 están en «1» (como ahora veremos), y si sobre la entrada E no se aplica tensión alguna, R1 aplica un «1» lógico sobre la entrada de la puerta P1. En tales condiciones, la salida de dicha puerta es «0». La puerta P2 invertirá este nivel lógico, apareciendo un «1» en S2, como se había supuesto.

Por otro lado, al ser «0» la salida de P1, el condensador C1 se encuentra descargado, por la resistencia R2 no circulará corriente alguna, y la entrada de P3 será también un «0» lógico. Por tanto, y gracias a la inversión realizada por P3, la salida S1 será un «1», tal y como se dijo al principio. Estamos en presencia del estado estable del circuito, en el que puede permanecer indefinidamente.

Cuando se aplica un «0» a la entrada E, la salida de P1 irá a nivel «1» y, automáticamente, la salida S2 irá a nivel «0». Puesto que la carga de un condensador no puede ser variada instantáneamente, sino que se trata de un proceso que consume un cierto tiempo, y carga y tensión están directamente relacio-

Figura 1. Circuito básico.

nadas ( $Q = C \cdot V$ ), tal tensión presentará una cierta «inercia» eléctrica en su variación.

Esta «inercia» es la causante de que el salto brusco de tensión de «0» a «1» en la salida de P1 no pueda ser absorbido instantáneamente por el condensador C1, por lo que el salto pasará a su través y se aplicará a la entrada de P3, cuya salida adoptará el nivel «0».

El nivel de salida «0» de P3 se lleva

a la puerta P1, con lo que la salida de esta última permanecerá en «1» aunque el nivel «0» desaparezca de la entrada E. Este extremo es muy importante, y muestra que el propio circuito «cierra» la puerta de entrada mientras se desarrolla el proceso que a continuación se explica.

#### Estado semiestable

Habíamos dejado al circuito recién disparado, con la salida de P1 en nivel lógico «1». Esto equivale a decir que sobre el circuito serie C1-R2 está aplicada la tensión de alimentación. El condensador C1 comenzará a cargarse. Conforme adquiere carga, la tensión entre sus terminales aumenta, con lo que la tensión sobre la resistencia R2 disminuye. Puesto que la tensión sobre R2 se aplica a la entrada de la puerta P3,

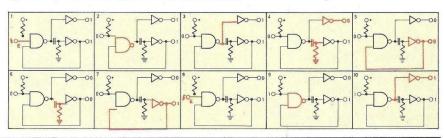

Figura 2. Secuencia de pasos en un monoestable.

ésta mantendrá su salida a nivel lógico «0» mientras que en su entrada haya una tensión igual o superior a la de umbral de cambio de estado. Llegará un momento en que la tensión sobre la entrada de P3 disminuya a un valor tal que dicha puerta lo interprete como nivel lógico «0», momento en que basculará y su salida se hará «1» de nuevo. Obsérvese que la salida de P3 (la llamada S1) ha permanecido en estado lógico «0» desde el disparo del circuito (provocado por la aplicación a la entrada E de un nivel «0») hasta que la carga del condensador C1 ha adquirido un cierto valor. Tal período de tiempo depende solamente de los valores de C1 y R2, y puede calcularse, aproximadamente, con ayuda de la expresión:

$T_0 = 0.7 \cdot R2 \cdot C1$  en la que  $T_0$  viene medida en milisegundos, si R2 se expresa en kilohmios y C1 en microfaradios.

## El retorno

Una vez que P3 ha basculado a su estado inicial (S1 en «1» lógico), la «llave» que dejaba insensible la puerta P1 a las variaciones de la entrada E deja de existir, y P1 puede volver a ser gobernada por dicha entrada.

Si cuando S1 vuelve a «1», la entrada E aún sigue en «0», la salida de P1 no variará, y tampoco lo hará la salida S2 (se mantendrá en «0»). El condensador C1 se seguirá cargando y el circuito no experimentará nuevos cambios hasta que E vaya a «1» de nuevo (también lo hará S2) y el circuito se encuentre en su estado estable.

Si, por el contrario, cuando P3 bascula al estado inicial, la entrada E ya ha retornado al nivel «1», sobre ambas entradas de la puerta P1 aparecerán sendos niveles «1», por

lo que su salida irá a «0». Esto provocará que S2 vaya a «1», y que el condensador C2 se descargue rápidamente a través de P1, con lo cual se volverá a la situación inicial. En resumen, el circuito es capaz de entregar un impulso de duración fija (determinada por R2 y C1) cualquiera que sea la duración del que se aplique a su entrada. Y también será capaz de entregar otro impulso cuya duración es, o igual a la del impulso de entrada, o a la del de duración fija (la que más grande sea).

Figura 3. Formas de onda en distintos puntos.

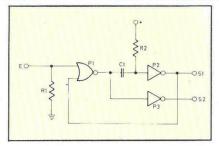

El funcionamiento de un monoestable de este tipo es muy similar al de otro construido con puertas NAND, aunque existen diferencias de niveles lógicos de trabajo de las puertas, tal como ahora veremos. En la figura 1 se muestra el circuito básico utilizado.

Cuando el circuito se encuentra en reposo, ambas salidas, S1 y S2, están en nivel lógico «0». Las dos entradas de P1 se encuentran en «0», una de ellas gracias a R1 (conectada a masa), y la otra por estar unida a la salida S1. Por tanto, la salida de

Figura 1. Circuito básico con puertas NOR.

P1 será «1». Puesto que la entrada de P3 es «1», y dado que tal puerta es inversora, su salida será «0», que es, precisamente S2, y que se encuentra al nivel lógico que antes diiimos.

Por otro lado, y ya que la salida de P1 está en «1» (equivalente a una tensión igual a la de alimentación), el condensador C1 se encontrará descargado (ambas armaduras a una tensión igual a la de alimentación) y R2 aplicará un nivel «1» a la entrada de P2, con lo que su salida (la llamada S1) estará en «0», tal y como se había supuesto al principio.

## El disparo

El cambio de estado se provoca cuando sobre la entrada E se aplica

Figura 2. Secuencia de pasos en el monoestable

un nivel lógico «1». En ese momento, la salida de la puerta P1 irá a «0». Este nivel será invertido por la puerta P3 de forma que en la salida S2 se obtenga un «1».

El paso brusco de nivel «1» a «0» en la salida de P1 será transmitido a través de C1, dada la inercia que el condensador presenta en la variación de su carga (y de su tensión). Por tanto, en la entrada de P2 se aplicará un «0» y su salida (que es, precisamente, S1) irá a «1». Este nivel «cerrará» la puerta P1 ante cualquier variación en el nivel lógico de la entrada E, manteniendo un «0» en su salida.

Como la entrada de P2 está a nivel lógico «0» (su tensión es igual a la de masa), sobre la resistencia R2 está aplicada la tensión de alimentación, por lo que tenderá a circular a su través una cierta corriente. Tal corriente irá cargando el condensador C1, de manera que la tensión a su través irá aumentando en forma exponencial. En consecuencia, la tensión en la entrada de P2 irá también aumentando.

Cuando la tensión sobre la entrada de P2 alcance un valor tal que sea interpretado como nivel lógico «1», su salida irá a «0» de nuevo, liberando a P1 de la «llave» que sobre

Figura 3. Circuito práctico. En S2 se obtiene un nivel «1» cuando el conmutador se pasa de REP a ACT, evitando el «efecto de rebote».

ella tenía aplicada P2. La salida S1 quedará como en reposo, es decir, en nivel «0».

## La vuelta al reposo

Si cuando P2 ha basculado a su nivel de reposo (S1 = «0»), sobre la entrada E ya ha desaparecido el nivel «1» que disparó el circuito, a las entradas de la puerta P1 habrá aplicados sendos niveles «0», por lo que su salida irá a «1». Este nivel provocará el cambio de S2 a «0», y además descargará rápidamente el condensador C1, quedando el circuito como en su condición inicial. Si al bascular la salida de P2 a «0», sobre la entrada de E aún subsiste un «1» lógico, el resto del circuito permanecerá en el mismo estado;

el condensador C1 seguirá cargándose y los niveles lógicos en las salidas serán los mismos (S1 = «0»; S2 = «1»). Esta situación sólo cesará cuando la entrada E vuelva a su nivel lógico inicial «0», en cuyo momento ocurrirán los procesos descritos en el párrafo anterior (ver figura 2).

### Circuitos prácticos

El tiempo que la salida S1 permanece en nivel «1» después de haber sido aplicado un nivel «1» en la entrada E se calcula como:

$$T_0 = 0.7 \cdot R2 \cdot C1$$

mientras que sobre la salida S2 existe nivel «1» durante, al menos, un tiempo  $T_0$ ; tal tiempo puede prolongarse hasta que la entrada E retorne a «0».

En la figura 3 se muestra un circuito basado en el montaje explicado y que entrega un impulso de duración fija e igual a 0,1 segundos en la salida S1, y un nivel «1» en su salida S2 cuando se acciona el conmutador de la posición REP a la ACT. Con tal circuito se evita el efecto de «rebote» (sólo en su flanco de subida) que suelen presentar los conmutadores mecánicos.

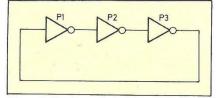

# Función y velocidad

Siempre que se habla de puertas lógicas, lo habitual es referirse a la función que realizan, sin mencionar la velocidad a que efectúan tal función. Evidentemente, la salida de una puerta inversora tardará un cierto tiempo en cambiar su nivel lógico cuando lo hace su entrada.

En general, tal tiempo es lo suficientemente reducido como para no tenerle en cuenta, pues, de otra forma, habría que emplear otra puerta más «rápida», y el problema quedaría solucionado. Ese tiempo suele denominarse de retardo.

El tiempo de retardo supone una limitación práctica importante, puesto que delimita la velocidad máxima o la frecuencia de trabajo más elevada a la que puede hacerse funcionar un dispositivo lógico. Cuanto más compleja es una función, mayor tiempo de retardo presenta, y a menor frecuencia má xima de trabajo podrá funcionar correctamente.

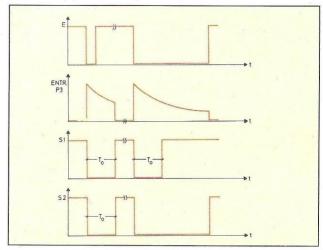

Sin embargo, no todos son inconvenientes, y una ventaja práctica puede obtenerse de tal «limitación». Supongamos que se montan tres inversores en serie, de tal

Figura 1. Circuito oscilador básico

forma que la salida del último esté conectada con la entrada del primero (fig. 1).

Imaginemos que, en un instante dado, la entrada de la puerta P1 se

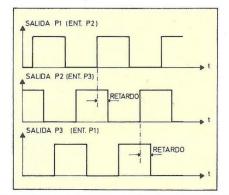

Figura 2. Formas de onda obtenidas del circuito básico.

hace de valor lógico «O». Su salida tenderá a hacerse «1», aunque para ello consuma un cierto tiempo. Puesto que tal salida es la entrada de P2, la salida de esta última se hará «O», después de un cierto tiempo. La puerta P3 invertirá su entrada, y su salida se hará «1».

En este punto, vemos que un «0» en la entrada de P1 ha acabado por formar un «1» en la salida de P3, que, a su vez, es la entrada de P1. Tal proceso no es incongruente, puesto que entre el «0» original y el «1» formado ha transcurrido un cierto tiempo.

# Señal formada

¿Cómo se desarrollan los acontecimientos a partir de esta situación? Pues de forma similar, ya que el «1» en la entrada de P1 desencadenará una nueva sucesión de «ceros» y «unos» hasta que en tal entrada aparezca un «0». Nuevo proceso, que culminará con un «1» en la entrada de P1, y así sucesiva e indefinidamente.

Como puede observarse, se está autogenerando una oscilación que tiene forma de *onda cuadrada*, con sucesivos niveles «1» y «0». Tal os-

cilación puede recogerse de cualquiera de los puntos del circuito (entrada o salida de una de las tres puertas), ya que son todos ellos eléctricamente equivalentes. La única diferencia hallada será un desfase o retraso, según el punto que se considere (fig. 2).

### Frecuencia de oscilación

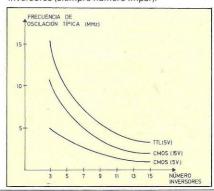

Parece claro que la frecuencia de la oscilación generada depende directamente del tiempo de retardo de cada puerta inversora. Un ciclo de la señal estará compuesto por dos «pases» completos de los fenómenos descritos. Esto es, después de seis tiempos de retardo individuales (suponiendo que son todos iguales). Los retardos encontrados en la práctica dependen del tipo de tecnología en que están construidos los inversores. Para TTL, el valor típico se sitúa sobre los 10 nseg, mientras que para CMOS varía entre 15 y 30 nseg, según la tensión con que se alimente el circuito. Como valores prácticos, pueden generarse frecuencias típicas de unos 16 MHz con TTL y de 5 a 11

MHz con CMOS (según la tensión de alimentación).

El retardo puede aumentarse (y la frecuencia disminuirse) intercalando mayor número de inversores en la cadena, con la condición de que el total empleado sea un número *impar*. Con cinco inversores TTL la frecuencia típica obtenida será de 10 MHz, mientras que con siete CMOS podrá obtenerse un valor comprendido entre 2,5 y 5 MHz (fig. 3).

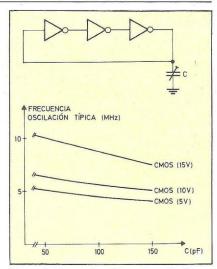

También pueden conseguirse ma-

**Figura 3.** Frecuencias típicas de oscilación según el tipo de circuito empleado y el número de inversores (siempre número impar).

Figura 4. Frecuencias típicas de oscilación según el valor de la capacidad y de la tensión de alimentación.

yores retardos conectando condensadores entre las salidas de las puertas y masa. Cuanto mayor sea el número de condensadores y la capacidad de los mismos, menor será la frecuencia de oscilación. Con este método puede, incluso, ajustarse la frecuencia al valor deseado (fig. 4).