Unidad Didáctica Secuenciales

# FONDO SIFFORMACIÓN

# rograma de ormación Abierta y le ible

Obra colectiva de FONDO FORMACION

**Coordinación** Servicio de Producción Didáctica de Fondo Formacion

(Dirección de Recursos)

**Diseño y maquetación** Servicio de Publicaciones de Fondo Formacion

#### © FONDO FORMACION - FPE

No está permitida la reproducción total o parcial de este libro, ni su tratamiento informático, ni la transmisión de ninguna forma o por cualquier medio, ya sea electrónico, mecánico, por fotocopia, por registro u otro método, sin el permiso previo y por escrito de los titulares del Copyright.

Depósito Legal AS -1953-2001

# Unidad Didáctica Secuenciales

Los sistemas en los que el estado de sus salidas depende del de las entradas y de estados anteriores que, de alguna manera han sido memorizados, se denominan "sistemas secuenciales."

Los sistemas secuenciales son un tipo de sistemas electrónicos digitales capaces de memorizar cierta información, ya que, en un sistema secuencial, cuando se repite una misma combinación de entradas, la salida puede ser diferente dependiendo de la historia pasada del circuito.

Para que un circuito recuerde la historia pasada, o secuencia, y pueda determinar el estado de su salida en función de esa historia, se necesitan circuitos electrónicos capaces de memorizarla. Los circuitos más simples con capacidad de memoria son los biestables, y de su estudio vamos a ocuparnos en esta unidad.

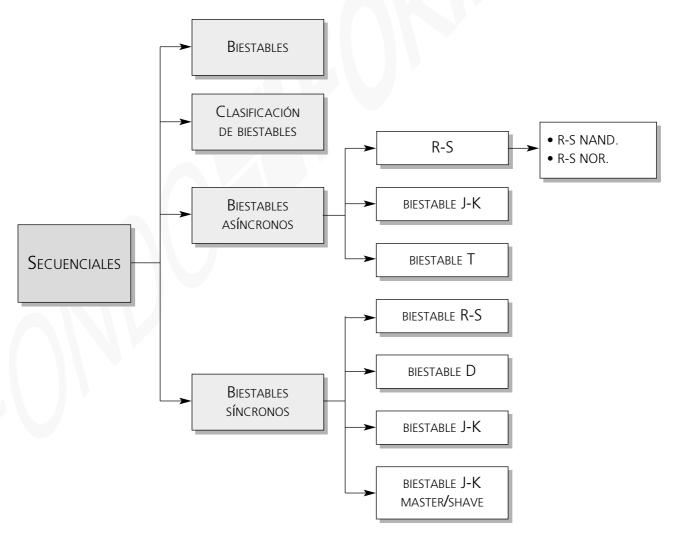

En esta unidad veremos los siguientes contenidos:

- Biestables.

- Clasificación de biestables.

- Biestables asíncronos.

- Biestables síncronos.

### Tus objetivos

Al finalizar el estudio de esta unidad, serás capaz de:

- Enumerar diferentes tipos de biestables.

- Analizar el comportamiento lógico de los biestables.

- Implementar biestables con puertas lógicas.

- Utilizar la simbología de este tipo de circuitos.

- Diferenciar biestables por el modo de disparo.

- Manejar la terminología de los circuitos secuenciales.

## Esquema de estudio

#### **Biestables**

Los biestables son **circuitos lógicos elementales** capaces de permanecer en uno de sus dos estados estables, aún después de desaparecer la causa que provocó el paso al estado actual; es decir, son capaces de **almacenar una información binaria.**

La característica de retención de sus dos posibles estados hacen de los biestables la célula elemental de memoria que constituye la base para la construcción de sistemas secuenciales.

Los biestables son los elementos básicos de memoria.

#### Clasificación de biestables

Existe una gran variedad de biestables y se pueden clasificar de muy diversas maneras:

- Según la lógica de disparo\*, tenemos biestables RS, JK, T y D.

- Dependiendo del tipo de disparo, los tenemos por nivel y por flanco.

- Atendiendo al sincronismo de disparo, tenemos biestables asíncronos y síncronos. Dentro de los biestables síncronos, podemos diferenciar los que son disparados por nivel o por flancos.

Con todos estos parámetros se pueden encontrar biestables que atienden a todas las clasificaciones mencionadas, así por ejemplo podemos tener un biestable JK síncrono, disparado por flanco y con entradas asíncronas.

#### Biestables asíncronos

Son biestables en los que las señales de entrada son válidas en todo momento. Los cambios de las salidas se producen en los mismos instantes en que se modifican las entradas (no tenemos en cuenta los retardos de las propias puertas del circuito).

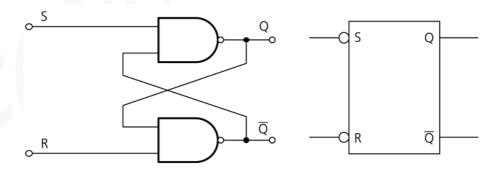

#### 1. Biestable R-S

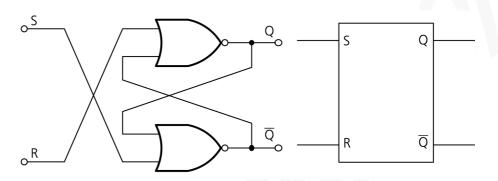

El circuito va a disponer de dos entradas, R y S, y dos salidas Q y  $\overline{Q}$ .

Hay dos formas de implementar\* este tipo de biestable, dependiendo del tipo de puerta empleado.

#### **R-S con puertas NOR**

En la figura 1, puedes ver la estructura del biestable básico R-S realizado con puertas NOR.

$Q^t$  $O^{t+1}$ R S 0 0 0 0 0 0 1 1 0 1 0 1 0 1 1 1 0 0 0 1  $\Omega$ 1 0 1 1 1 0 IND 1 1 1 IND

Fig. 1: Circuito lógico y símbolo del biestable R-S NOR.

El modo de funcionamiento de este biestable queda reflejado en la tabla de verdad del margen.

Leyendo la tabla de verdad puedes ver que si en la entrada S aparece un nivel alto, la salida Q pasa a nivel alto si previamente estaba en nivel bajo, o permanece en nivel alto si anteriormente estaba en ese estado.

Tabla de verdad del biestable R-S NOR

- R: es la entrada **reset** o puesta a 0 lógico.

- S: es la entrada de **set** o puesta a 1 lógico.

- *Q*<sup>t</sup>: es la salida Q presente antes de un cambio.

- $Q^{t+1}$ : es la salida Q un instante después de un cambio.

Si se presenta un nivel alto en la entrada *R*, la salida *Q* se pone a nivel bajo si antes estaba en nivel alto, o permanece en nivel bajo si previamente ya estaba en ese estado.

Si las dos entradas están a nivel bajo, la salida Q no cambia de estado, permaneciendo en el que estaba anteriormente.

Cuando ambas entradas, R y S, se ponen a 1, las dos salidas Q y  $\overline{Q}$  se ponen a cero, lo cual es una situación anómala, ya que el biestable pierde su condición como tal, puesto que ha de presentar dos salidas complementarias. Además, si estando ambas entradas a nivel alto y simultáneamente se ponen a nivel bajo, el estado final de las salidas es imprevisible y depende de la velocidad de respuesta de las puertas. Por eso decimos que **la salida es indeterminada cuando ambas entradas se encuentran a nivel alto.** Físicamente la respuesta a esta situación será una, pero depende de la propia fabricación del integrado. Si una puerta es más rápida que otra, la respuesta será de una manera y viceversa, con lo cual es una situación no permitida.

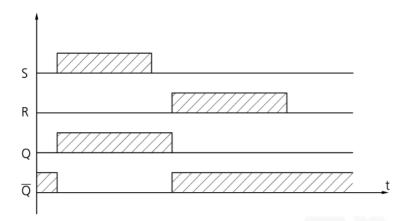

Los **diagramas de tiempos** son una forma de representar el comportamiento de los sistemas secuenciales, y mediante ellos se puede explicar su funcionamiento. En la figura 2, puedes ver el diagrama de tiempos del biestable R-S donde, para una mejor comprensión, no se han tenido en cuenta los tiempos de retardo de las puertas que conforman el biestable.

Fig. 2: Diagrama de tiempos del biestable R-S.

Así, puedes observar, en la figura 2, que cuando la entrada *S* se pone a nivel alto, la salida *Q* pasa a nivel alto y cuando la entrada R pasa a nivel alto, la salida *Q* se pone a nivel bajo; por tanto, es un biestable activado por niveles altos.

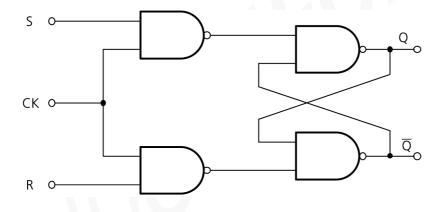

#### **R-S con puertas NAND**

El circuito básico de un biestable R-S también se puede realizar con dos puertas NAND, como ves en la figura 3.

Fig. 3: Circuito lógico y símbolo del biestable R-S NAND.

El análisis del circuito es similar al anterior, pero, en este caso, la combinación prohibida es R = S = O.

Tal como ves, en la simbología decimos que las entradas son ahora activas a nivel bajo.

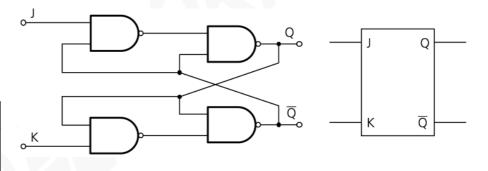

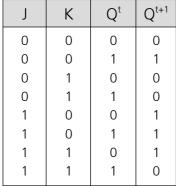

#### 2. Biestable JK asíncrono

El biestable J-K deshace la indeterminación del R-S, obligando a que las salidas cambien de estado ante la activación de las dos entradas al mismo tiempo.

En este biestable hay una entrada llamada J que realiza la función de set (puesta a 1), y otra denominada K, que realiza la función de reset (puesta a cero). En la figura 4, puedes ver el circuito realizado con puertas NAND.

Fig. 4: Circuito lógico y símbolo del biestable J-K.

En el margen, puedes ver su tabla de verdad.

Observa que en la tabla de verdad ya no aparece la indeterminación en la salida cuando las dos entradas están a 1 lógico. La salida del biestable en esa situación cambia de estado.

Tabla de verdad del biestable J-K.

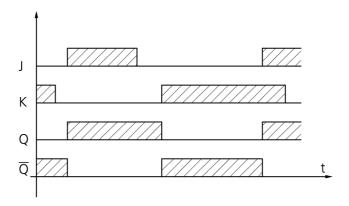

En la figura 5 se representa el diagrama de tiempos.

Fig. 5: Diagrama de tiempos del biestable J-K.

#### 3. Biestable T

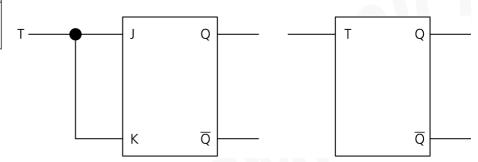

En la figura 6 puedes ver el biestable T obtenido a partir de un J-K. Sólo dispone de una entrada, ya que hemos unido las dos entradas del biestable J-K, formando así un nuevo biestable denominado T.

| Т | $Q^{t+1}$      |

|---|----------------|

| 0 | Q <sup>t</sup> |

| 1 | Q <sup>t</sup> |

Tabla de verdad del biestable T.

Fig. 6: Circuito lógico y símbolo del biestable T.

La tabla de verdad es la del margen izquierdo y –como puedes apreciar– cuando la entrada se activa, la salida cambia.

#### **Biestables síncronos**

Hay circuitos digitales en los que es necesario que los cambios de estado ocurran cuando una señal denominada de **reloj** esté presente; los biestables que tienen esta característica se denominan *síncronos*.

Gracias a la señal de reloj podemos hacer que los cambios de estado del biestable se realicen cuando tengamos la seguridad de que las señales de entrada deseadas están presentes.

Se denomina **entrada síncrona** a aquella que no cambia la salida por ella misma, sino que necesita que esté presente otra señal (la de reloj) para que se produzca el cambio de estado.

Con el objeto de disponer de circuitos más flexibles en los biestables síncronos existen otras señales denominadas **asíncronas** porque son capaces de modificar la salida del biestable sin necesidad de la señal de reloj.

Las señales asíncronas pueden ser dos: la **señal de** preset, que pone a 1 la salida del biestable independientemente del resto de señales de entrada o de reloj, y la **señal de** clear, que pone a 0 la salida del biestable también independientemente del resto de señales de entrada.

Por tanto, un biestable síncrono con entradas asíncronas puede funcionar de manera síncrona sólo cuando las entradas asíncronas no actúan.

Dentro de los biestables síncronos debemos distinguir los que son disparados **por nivel** y los disparados **por flancos.** Los veremos a continuación.

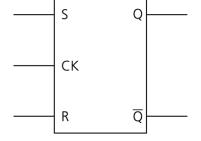

#### 1. Biestable R-S síncrono

Es un biestable en el que –como puedes ver en el circuito lógico de la figura 7–, las entradas operan sólo cuando el reloj, CK, se encuentra a nivel alto, en este caso.

Fig. 7: Biestable R-S activo por nivel alto.

El símbolo lógico es el de la figura 8 que –como ves– lleva una señal de reloj, las dos señales S y R como entradas, y las dos salidas complementarias.

Fig. 8 Símbolo lógico de un biestable R-S activo por nivel alto.

#### 2. Biestable D síncrono

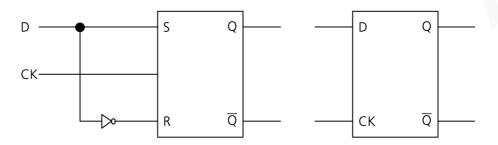

Si al biestable R-S le añadimos un inversor puesto como en la figura 9, obtenemos otro biestable llamado *D*, que es síncrono por naturaleza, por eso lleva además la señal de reloj.

CK

D

Q<sup>t+1</sup>

0

X

Q<sup>t</sup>

1

0

0

1

1

1

Tabla de verdad del biestable D.

Fig. 9. Circuito lógico y símbolo del biestable D activo por nivel.

En el biestable tipo *D*, la salida sigue a la entrada, es decir, cuando en la entrada tenemos un 1, en la salida aparece un 1, y cuando la entrada sea un 0, en la salida aparece un 0, siempre que el reloj esté a nivel alto –como puedes apreciar en su tabla de verdad.

En los biestables disparados por flancos, las entradas solamente son activas cuando la señal de reloj está cambiando de nivel.

Si las entradas actúan cuando el reloj pasa de nivel bajo a nivel alto, decimos que el biestable es activo en el **flanco de subida.**

Cuando las entradas actúan mientras el reloj pasa de nivel alto a nivel bajo, se dice que el biestable es activo en el **flanco de bajada.**

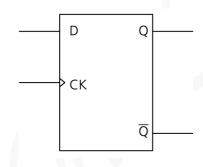

En la figura 10 se representa el símbolo de un biestable D activo por flanco de subida.

Fig. 10 Biestable D activo por el flanco de subida.

#### 3. Biestable J-K síncrono

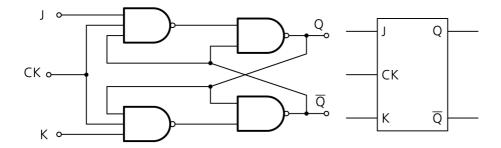

En la figura 11 puedes ver un biestable de este tipo que, como todos los biestables síncronos, lleva una entrada de reloj que habilita las entradas *J* y *K*.

Fig. 11: Circuito y simbología de un biestable J-K activo por nivel.

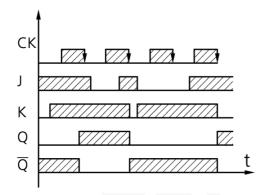

En la figura 12 puedes ver un diagrama de tiempos de un biestable J-K activado por flanco de bajada. Los cambios en las salidas se producen en el flanco negativo del reloj.

Fig. 12: Temporización de un J-K síncrono por flanco de bajada.

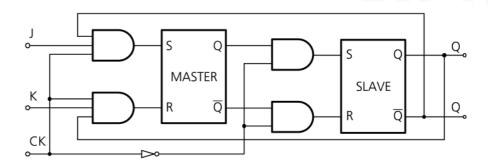

#### 4. Biestable J-K "master slave"

Estos biestables se basan en aislar la salida de la entrada y están formados por dos biestables (el maestro y el esclavo) y dos circuitos lógicos de inhibición que se encuentran siempre en estados distintos debido al inversor, como puedes ver en la figura 13.

Fig. 13: Biestable J-K master-slave.

El circuito funciona del modo siguiente:

Con el reloj a nivel bajo, la información presente en las entradas no actúa sobre el biestable maestro; en cambio el biestable esclavo recibe la información del maestro para ponerla en las salidas.

Cuando el reloj pase a nivel alto, el maestro acepta las señales de entrada, mientras que el esclavo mantiene en sus salidas el valor que le impuso el maestro cuando la señal de reloj estaba a nivel bajo.

Al producirse la transición de nivel alto a bajo en la señal de reloj, el maestro queda aislado de nuevo y su estado será el que le hayan dejado las entradas. Al mismo tiempo, el estado del maestro pasará al esclavo, permaneciendo así hasta que llegue el nuevo impulso de reloj.

Si consideras que has concluido el estudio de esta unidad, intenta responder a las siguientes cuestiones de autoevaluación.

# Cuestiones de autoevaluación

Completa el texto con las palabras siguientes:

preset, síncronas, biestables, asíncrona, entrada, señales, clear

| En los síncronos,                | , además de las entradas                     |

|----------------------------------|----------------------------------------------|

| pueden existir otras             | denominadas <i>asíncronas.</i> La señal de   |

| se encarga de                    | poner a uno lógico la salida del biestable,  |

| independientemente del resto d   | e señales de, y la señal                     |

| de se enc                        | arga de ponerlo a cero. Con lo cual un bies- |

| table síncrono puede funcionar o | le manera                                    |

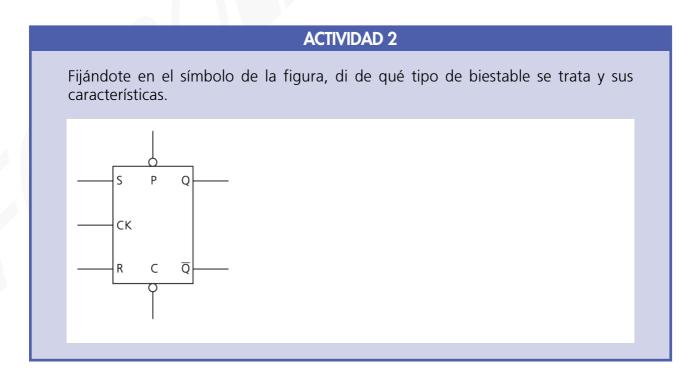

2 El símbolo que aparece en la figura, ¿qué tipo de biestable representa?

# Respuestas a las actividades

# **ACTIVIDAD 1**

La tabla de verdad para el biestable R-S NAND, es la siguiente:

| R | S | Q <sup>t</sup> | Q <sup>t+1</sup> |

|---|---|----------------|------------------|

| 0 | 0 | 0              | IND              |

| 0 | 0 | 1              | IND              |

| 0 | 1 | 0              | 0                |

| 0 | 1 | 1              | 0                |

| 1 | 0 | 0              | 1                |

| 1 | 0 | 1              | 1                |

| 1 | 1 | 0              | 0                |

| 1 | 1 | 1              | 1                |

## **ACTIVIDAD 2**

Podemos decir que se trata de biestable *R-S* síncrono activo por nivel alto y con entradas asíncronas de *preset* y *clear* activas a niveles bajos.

### Respuestas a las cuestiones de autoevaluación

Tu respuesta será:

1

En los **biestables** síncronos, además de las entradas **síncronas** pueden existir otras **señales** denominadas asíncronas. La señal de preset se encarga de poner a uno lógico la salida del biestable, independientemente del resto de señales de **entrada**, y la señal de clear se encarga de ponerlo a cero. Con lo cual, un biestable síncrono puede funcionar de manera **asíncrona**.

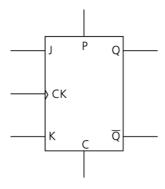

El símbolo representa un biestable J-K síncrono disparado por el flanco de subida que, además, presenta entradas asíncronas activas a nivel alto.

2

# Resumen de Unidad

**Biestables** Son los elementos básicos de memoria.

Podemos mencionar los tipos RS, JK, T y D con sus diferentes variantes.

Para saber el funcionamiento de un biestable, podemos servirnos de su tabla de verdad o del diagrama de tiempos.

**Biestables asíncronos**

Son aquellos que no llevan reloj y, por tanto, sus entradas pueden ser activas siempre.

**Biestables síncronos**

Son aquellos que llevan reloj y pueden llevar señales asíncronas.

La señal de *preset* es asíncrona, y es capaz de poner a uno lógico la salida del biestable.

La señal de *clear* también es asíncrona y se encarga de poner a cero lógico la salida del biestable.

Los biestables síncronos pueden ser disparados por nivel o por flancos.

En los biestables disparados por flancos las entradas solamente son activas cuando la señal de reloj está cambiando de nivel.

Los biestables master slave están formados por dos biestables y una circuitería lógica auxiliar y son disparados por flancos. En un biestable de este tipo las salidas están aisladas de las entradas.

|                                                    | , 6,12,6,2,1,0,10,10,10,10,10,10,10,10,10,10,10,10    |

|----------------------------------------------------|-------------------------------------------------------|

| Notas                                              |                                                       |

|                                                    |                                                       |

|                                                    |                                                       |

|                                                    |                                                       |

|                                                    |                                                       |

|                                                    |                                                       |

|                                                    |                                                       |

|                                                    |                                                       |

| Vocabulario                                        |                                                       |

| <b>Disparo:</b> es la señal exterior que e estado. | s necesario aplicar a un biestable para que cambie de |

Implementar: realizar, hacer, activar.

# FONDO HI FORMACION